# HPC Virtualization with Xen on Itanium

Håvard K. F. Bjerke

July 18, 2005

#### Abstract

The Xen Virtual Machine Monitor has proven to achieve higher efficiency in virtualizing the x86 architecture than competing x86 virtualization technologies. This makes virtualization on the x86 platform more feasible in High-Performance and mainframe computing, where virtualization can offer attractive solutions for managing resources between users. Virtualization is also attractive on the Itanium architecture. Future x86 and Itanium computer architectures include extensions which make virtualization more efficient. Moving to virtualizing resources through Xen may ready computer centers for the possibilities offered by these extensions.

The Itanium architecture is "uncooperative" in terms of virtualization. Privilege-sensitive instructions make full virtualization inefficient and impose the need for *para-virtualization*. Para-virtualizing Linux involves changing certain native operations in the guest kernel in order to adapt it to the Xen virtual architecture. Minimum para-virtualizing impact on Linux is achieved by, instead of replacing illegal instructions, trapping them by the hypervisor, which then emulates them. *Transparent para-virtualization* allows the same Linux kernel binary to run on top of Xen and on physical hardware.

Itanium *region registers* allow more graceful distribution of memory between guest operating systems, while not disturbing the Translation Lookaside Buffer. The *Extensible Firmware Interface* provides a standardized interface to hardware functions, and is easier to virtualize than legacy hardware interfaces.

The overhead of running para-virtualized Linux on Itanium is reasonably small and measured to be around 4.9 %. Also, the overhead of running transparently para-virtualized Linux on physical hardware is reasonably small compared to non-virtualized Linux.

#### Preface

This master's thesis was written at the European Organization for Nuclear Research (CERN), while working for the CERN OpenLab for DataGrid Applications collaboration. The work is a continuation of previous research at CERN and NTNU, which has been conducted with fellow student Rune Andresen. We have looked into the application of virtualization with Xen in CERN's computational resources. CERN's computational Grid is being developed mainly for the purpose of collecting and analyzing data which will be produced by detectors in the Large Hadron Collider (LHC), after its experiments commence in 2007.

Most of the work described in this thesis has been conducted by Dan Magenheimer at HP Labs Fort Collins, the Xen Team at the University of Cambridge and affiliates of Intel and SGI. My work at the CERN OpenLab has been in assisting Dan Magenheimer in porting Xen to the Itanium architecture. This has involved testing, debugging and analyzing Xen and developing support for multiple domains on Itanium.

I thank Sverre Jarp, Anne C. Elster and Dan Magenheimer for giving me the opportunity to work on this project; the developers on the Xen mailing list and, again, Dan, for long-distance, but helpful, e-mail discussions; Rune Andresen and Dan for helpful feedback on this thesis; and Andreas Hirstius for helping with hardware and fixing things that break.

# Contents

| 1        | Intr | Introduction                          |   |  |  |

|----------|------|---------------------------------------|---|--|--|

|          | 1.1  | Virtualization in the Grid            | 2 |  |  |

| <b>2</b> | Bac  | kground                               | 6 |  |  |

|          | 2.1  | 0                                     | 7 |  |  |

|          |      |                                       | 8 |  |  |

|          |      |                                       | 9 |  |  |

|          |      |                                       | 9 |  |  |

|          | 2.2  | The x86 Architecture                  | 1 |  |  |

|          |      | 2.2.1 Memory Management               | 1 |  |  |

|          |      | 2.2.2 Process Switching 1             | 3 |  |  |

|          |      | 2.2.3 The Floating Point Unit         | 3 |  |  |

|          |      | 2.2.4 Interrupts                      | 4 |  |  |

|          | 2.3  | The IA-64 Architecture 1              | 5 |  |  |

|          |      | 2.3.1 Key Features                    | 5 |  |  |

|          |      | 2.3.2 Registers                       | 7 |  |  |

|          |      | 2.3.3 Hardware Abstraction            | 7 |  |  |

|          |      | 2.3.4 Interrupts                      | 3 |  |  |

|          |      | 2.3.5 Memory Management               | 3 |  |  |

|          |      | 2.3.6 The Performance Monitoring Unit | 9 |  |  |

|          | 2.4  | Linux                                 | 0 |  |  |

|          |      | 2.4.1 Interrupts                      |   |  |  |

|          |      | 2.4.2 Time                            | 1 |  |  |

|          |      | 2.4.3 Processes                       | 3 |  |  |

|          |      | 2.4.4 Kernel Entry & Exit             |   |  |  |

|          |      | 2.4.5 Performance Monitoring          | 5 |  |  |

|          | 2.5  | Virtualization                        |   |  |  |

|          | -    | 2.5.1 Virtual Machine Monitors        |   |  |  |

|          | 2.6  | Xen Virtual Machine Monitor           | 8 |  |  |

|          |      | 2.6.1 Paravirtualization              |   |  |  |

|          |      | 2.6.2 Event Handling                  | 0 |  |  |

|          |      | 2.6.3 Memory Management               |   |  |  |

|          |      | 2.6.4 Time                            |   |  |  |

| •        |      |                                       | • |  |  |

|          |      | lysis 32                              |   |  |  |

|          | 3.1  | Virtualization on Intel Architecture  |   |  |  |

|          | 3.2  | The Xen Hypervisor                    |   |  |  |

|          |      | 3.2.1 Para-virtualization             | ö |  |  |

|              |                           | 3.2.2 System Startup                                                                                                                       |   |  |

|--------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|              |                           | 3.2.3 Memory Management                                                                                                                    |   |  |

|              |                           | 3.2.4 Hypercalls                                                                                                                           |   |  |

|              |                           | 3.2.5 Event Channels                                                                                                                       |   |  |

|              |                           | 3.2.6 Time and Scheduling $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 43$                                                     |   |  |

| 4            | 4 IA-64 Implementation 46 |                                                                                                                                            |   |  |

| 4.1 Analysis |                           |                                                                                                                                            |   |  |

|              |                           | 4.1.1 Privilege-Sensitive Instructions                                                                                                     |   |  |

|              |                           | 4.1.2 Optimized Para-virtualization                                                                                                        |   |  |

|              |                           | 4.1.3 Transparent Para-virtualization                                                                                                      |   |  |

|              |                           | 4.1.4 Memory Management                                                                                                                    |   |  |

|              |                           | 4.1.5 Hypercalls                                                                                                                           |   |  |

|              |                           | 4.1.6 Virtual Hash Page Table                                                                                                              |   |  |

|              |                           |                                                                                                                                            |   |  |

|              | 4.0                       | 8                                                                                                                                          |   |  |

|              | 4.2                       | Para-virtualization                                                                                                                        |   |  |

|              | 4.3                       | Optimized Para-virtualization                                                                                                              |   |  |

|              | 4.4                       | Memory Management                                                                                                                          |   |  |

|              | 4.5                       | Firmware Interface Emulation                                                                                                               |   |  |

|              | 4.6                       | $Events \dots \dots$                 |   |  |

|              | 4.7                       | Further Work                                                                                                                               |   |  |

| <b>5</b>     | Per                       | ormance Analysis 59                                                                                                                        | 1 |  |

|              | 5.1                       | Experimental Environment                                                                                                                   |   |  |

|              | 5.2                       | Methodology                                                                                                                                |   |  |

|              |                           | 5.2.1 Build Benchmark                                                                                                                      | 1 |  |

|              |                           | 5.2.2 Instrumentation $\ldots \ldots 61$ |   |  |

|              | 5.3                       | Results                                                                                                                                    |   |  |

|              |                           | 5.3.1 Build Benchmark                                                                                                                      |   |  |

|              |                           | 5.3.2 Instrumentation $$                                                                                                                   |   |  |

|              |                           |                                                                                                                                            |   |  |

| 6            | Rel                       | ted Work 64                                                                                                                                |   |  |

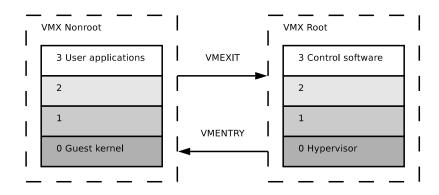

|              | 6.1                       | Intel Virtualization Technology                                                                                                            |   |  |

| 7            | Con                       | clusion 67                                                                                                                                 |   |  |

| Δ            | Reo                       | sters 68                                                                                                                                   |   |  |

| п            | -                         | Some Essential x86 Registers                                                                                                               |   |  |

|              |                           | Some Essential IA-64 Registers                                                                                                             |   |  |

|              | A.2                       | Joine Essential IA-04 Registers                                                                                                            |   |  |

| В            | Inst                      | uction Set Architectures 70                                                                                                                |   |  |

|              | B.1                       | Some Essential x86 Instructions                                                                                                            |   |  |

|              | B.2                       | Some Essential IA-64 Instructions                                                                                                          |   |  |

| С            | Sou                       | ce Code 71                                                                                                                                 |   |  |

|              | C.1                       | Event Channel Hypercall                                                                                                                    |   |  |

|              | C.2                       | Hypercall Handlers in the Hypervisor                                                                                                       |   |  |

|              | C.3                       | Privileged Operation Counters                                                                                                              |   |  |

|              |                           | Paravirtualization                                                                                                                         |   |  |

|              |                           |                                                                                                                                            |   |  |

# List of Figures

| 1.1          | The grid layer stack.                                                                                                        | 4                                       |

|--------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1.2          | An alternative grid implementation.                                                                                          | 4                                       |

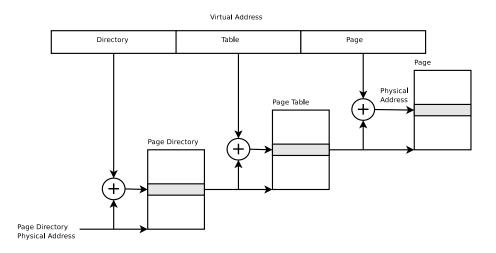

| 2.1          | Virtual address to physical address translation                                                                              | 10                                      |

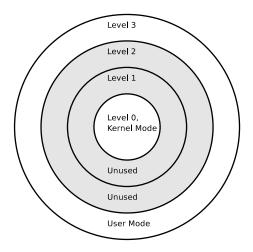

| 2.2          | Privilege separation in Linux on the x86 architecture                                                                        | 12                                      |

| 2.3          | The format of a bundle                                                                                                       | 16                                      |

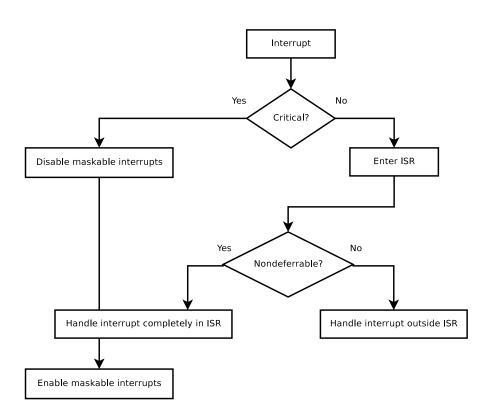

| 2.4          | Flowchart showing how interrupts are handled in Linux                                                                        | 22                                      |

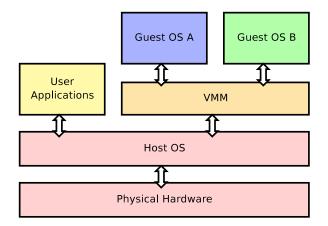

| 2.5          | Illustration of a VMM hosted on a host OS, running two guest                                                                 |                                         |

|              | OSs                                                                                                                          | 27                                      |

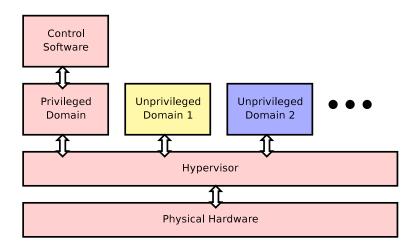

| 2.6          | The Xen hypervisor, hosting several domains.                                                                                 | 29                                      |

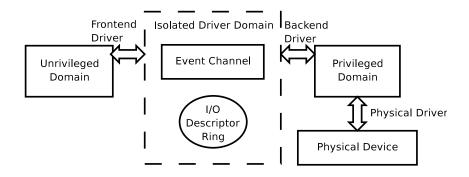

| 2.7          | Device virtualization in Xen.                                                                                                | 31                                      |

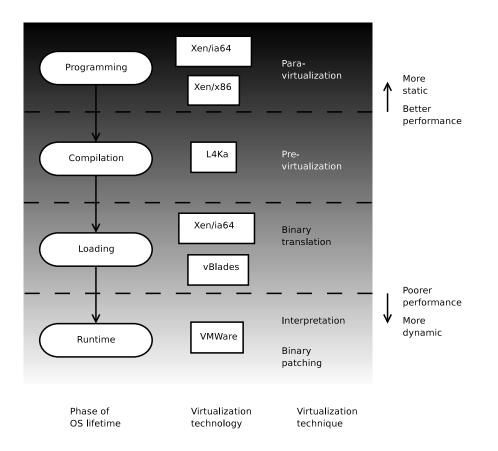

| 3.1          | Different methods of virtualization.                                                                                         | 34                                      |

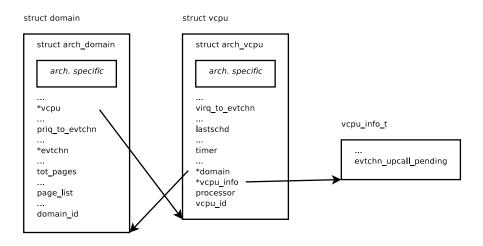

| 3.2          | The domain and vcpu data structures.                                                                                         | 36                                      |

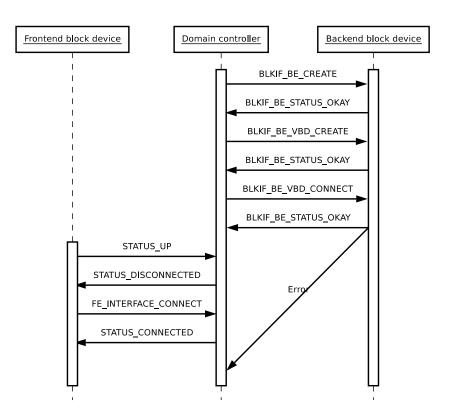

| 3.3          | Virtual block device initialization phase.                                                                                   | 44                                      |

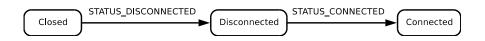

| 3.4          | The states and transitions of a frontend block device                                                                        | 44                                      |

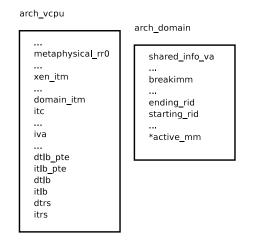

| 4.1          | Architecture specific parts of the domain and $\texttt{vcpu}$ data structures.                                               | 55                                      |

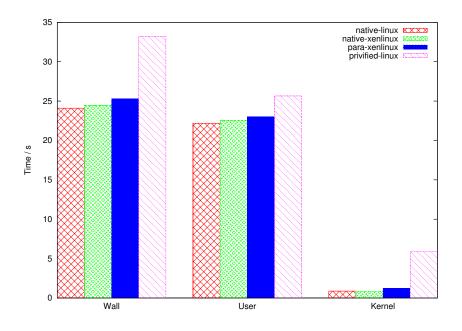

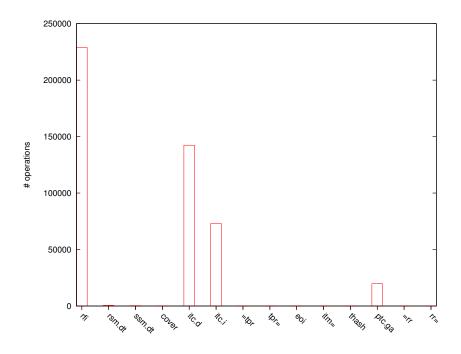

| $5.1 \\ 5.2$ | Bar chart showing the times measured in the build benchmark A chart over the number of para-virtualized operations executed. | $\begin{array}{c} 61 \\ 63 \end{array}$ |

| 6.1          | VT's VMX Root and Nonroot execution environments                                                                             | 66                                      |

# List of Tables

| 3.1 | The hypercalls of Xen/x86                               | 39 |

|-----|---------------------------------------------------------|----|

| 5.1 | The configuration of the OpenLab GRID testbed cluster   | 59 |

| 5.2 | Measured time when compiling Linux                      | 61 |

| 5.3 | Measured number of para-virtualized operations executed | 62 |

## Chapter 1

# Introduction

The Xen Virtual Machine Monitor is a virtualization project from the University of Cambridge. A presentation of the software is given in the paper "Xen and the Art of Virtualization" by Paul Barham et al.  $[B^+03]$ . Xen has recently gained much popularity partly due to its efficiency and free and open source licensing. The software developer and user community around the software has grown significantly over the last few months, due not only to its inherent benefits, but also to the attention it has received through popular computer journalism, which has further boosted its development and given momentum to the project. Powerful computer technology companies such as Sun Microsystems, Hewlett-Packard, Novell, Red Hat, Intel, Advanced Micro Devices (AMD), Voltaire and IBM, have also recognized the potential in the software and have become involved with the project [Sha05].

Experiences show that Xen is able to utilize commodity PC resources better than most VMMs, yielding close to native OS (Operating System) resource utilization [And04, B<sup>+</sup>03, BA04, F<sup>+</sup>04b]. Compared to similar technologies such as VMWare and User Mode Linux, the performance benefits prove to be significant in most applications. Xen achieves this performance advantage through an unconventional approach to virtualizing a computer, called *paravirtualization* [W<sup>+</sup>02]. One significant difference from traditional approaches is that this one allows only modified OSs to run on the virtual machine.

Traditional Virtual Machine Monitors (VMM) have aimed to be able to let any, or at least a few, OSs run unmodified in their VMM execution environment, that is, to provide a true virtualization of the architecture. This is necessary in order to run, for example, Windows XP on the VMM, since most regular users and software devolpers are not allowed nor able to modify the OS in order to have it run on custom architectures, be they virtual or real. With the emergence of main-stream open source licensed OSs, such as Linux and OpenBSD, software developers are given more freedom to modify the OSs so that they may possibly run on a given computer architecture. The Xen developers have taken advantage of this freedom by, instead of completely virtualizing the PC architecture, providing a more benificial Xen/x86 virtual architecture on which a modified OS may run.

Many novel applications for virtualization have emerged over the development of Xen as, more so than before, researchers and users now have access to a free, open, and efficient virtualization platform on cheap and powerful computers. Applications such as checkpointing, server consolidation and self-migrating OSs have become more feasible. Virtualization of computing resources is particularly attractive in HPC (High-Performance Computing), since this usually involves the sharing of computing resources among several users. By virtualizing resources, they may be shared between users more dynamically and securely.

Major computer chip manufacturers such as Intel and AMD, have also recognized the benefits of having multiple OS instances run simultaneously on a single processor. Recently, specifications for their Vanderpool (VT) and Pacifica processors have been released, which include facilities for enabling efficient true virtualization. Support for the Vanderpool virtualization architecture has already been implemented into Xen.

Xen has already shown to provide an efficient virtualization environment for x86 machines. The objective of this project is to attain and analyze a virtualization environment for the Itanium platform. This is important because grid computing resources consisting of Itanium machines can benefit from virtualization, as discussed in Section 1.1. The project involves assisting in the development of the Xen VMM for Itanium.

This master's thesis presents the work related to porting Xen to the Itanium architecture. Chapter 2 gives an introduction to some of the concepts used in further discussions in the thesis. Topics that are relevant for analysis of the virtualization of Itanium include the existing Xen implementation, current virtualization challenges on Intel architectures and specifics of the IA-64 architecture. These topics are discussed in Chapter 3. The implementation of Xen on Itanium is presented in Chapter 4. In order to evaluate the progress in terms of performance, Chapter 5 analyzes the performance of Xen/ia64. In Chapter 6, a few interesting projects that have relevance to Xen are discussed. Finally, Chapter 7 concludes the thesis.

### 1.1 Virtualization in the Grid

The construction of the Large Hadron Collider (LHC) at the European Organisation for Nuclear Research (CERN) is scheduled to complete in 2007. Many different high energy physics experiments will be performed in the LHC, by scientists from many parts of the world. An introduction to the LHC and its experiments can be found at [lhc05]. The particle detectors of the different experiments will generate massive amounts of data that need to be analyzed and stored on local and remote computing sites. It is estimated that roughly 15 PetaBytes of data will need to be processed and stored per year when the experiments start.

Computational grids are set to satisfy the demand for computing and storage resources, and many grid projects will be involved in the LHC experiments. Ian Foster and Carl Kesselman [FK] give a good introduction to grid computing. Also, previous work [Bje04] gives an overview of some important grid computing projects. One example grid project is the LHC Computing Grid project, which is being coordinated at CERN.

A computational grid can benefit from virtualization in a variety of ways. Xen is considered as a virtualization solution and has been evaluated for application in HPC in previous work with Rune Andresen [BA04]. The core parts of the LCG software stack has been ported to the Itanium architecture, which makes the LCG ready to employ Itanium machines. At this moment, three computing centers are currently contributing Itanium computers to the LCG [HC05]. By porting Xen to the IA-64 architecture, it will be one step closer to being realized in grid environments consisting of Itanium machines, such as the Itanium computers of the LCG and the OpenLab testbed at CERN.

Amit Singh [Sin04] presents an extensive list of virtualization benefits, which probably can be extended to include many more. Staying within the scope of HPC, a shorter list, focusing on HPC virtualization benefits, is presented in the following.

- A general trend in integrated circuit design is that the number of transistors that can fit per die area increases more rapidly than processor companies' capacity to produce new logic. Thus, copying existing logic from one CPU core into a multi-core CPU, allows new die area to be utilized. Multi-core CPUs, however, face the same limitations as symmetric multiprocessing (SMP) systems with regards to programming paradigm, as they essentially are shared memory parallel machines. Virtualization allows computing resources to be utilized with more flexibility. Different OSs may be run at the same time, and on a SMP system, OSs may be pinned to individual CPUs. With the arrival of multi-core CPUs, virtualization will allow these resources to be shared among users on a virtualized hardware level.

- Parties that have interest in grid computing resources, such as research institutions or commercial organizations, are organized into Virtual Organizations (VO). It is important that computations of one VO do not interfere with computations of another VO. Also, commercial VOs might want to keep their computations secret from competing VOs. Computations running in a virtualized environment may be *isolated* (see Section 2.5) while running on the same physical resources.

Nancy L Kelem and Richard J. Feiertag [KF91] argue that the isolation provided by a hardware virtualization mechanism can be more easily mathematically abstracted than the isolation provided by a traditional time-sharing OS's security model. The sufficiency of the hardware virtualization security model can be evaluated by looking at the isolation at the hardware level. Since hardware virtualization is a simpler mechanism than an OS and has fewer lines of code, its isolation can be more easily proven.

- When physicists submit a job to a grid, there is a probability that the job will fail. On a given grid resource, this probability increases with the amount of time the computation runs. The physicist may waste a lot of time or be delayed when after a while into the computation, finding that the computation has failed due to grid failure. Virtualization can allow the state of the entire OS to be stored in *checkpoints*, since the virtualization environment *encapsulates* the OS (see Section 2.5). In the case of a failure, the OS can then be brought back to the state it was in before the failure and continue from there.

- Also, because of encapsulation, a running OS with a computation can be *migrated* from one node in the grid to another and continue to run. This allows the load on the nodes to be balanced more dynamically, and

```

Computation

```

| Application | Portals, web services,               |   |

|-------------|--------------------------------------|---|

| Middleware  | Authentication, resource allocation, |   |

| Fabric      | OS, storage, sensors,                | / |

Figure 1.1: The grid layer stack.

```

OS image

```

| Application | Portals, web services,                    |   |

|-------------|-------------------------------------------|---|

| Middleware  | Authentication, resource allocation,      |   |

| Fabric      | virtualized hardware, storage, sensors, V | V |

Figure 1.2: An alternative grid implementation.

computations may be moved away from a node which is going down for maintenance.

• An illustration of the grid layer stack is shown in Figure 1.1. The *fabric* layer of the grid layer stack consists of, among others, OSs, and this is the execution environment in which grid computations effectively run. A computational job is first submitted by the user through a high level user interface, such as, for instance, a web portal, in the *Application* layer. Then the user is authenticated, and the job is allocated resources in the *Middleware* layer. Finally, the job is run on a node in the *Fabric* layer on the execution environment it provides. In the case of LCG, this is *Scientific Linux CERN* [slc05].

Grid computations depend on necessary libraries and dependencies being satisfied in these OSs. With virtualization, virtualized hardware is exposed at the fabric layer, as illustrated in Figure 1.2. Instead of submitting a computational job, the user may submit a complete OS with a filesystem, containing a computation. The submission and authentication proceeds as usual, but at the fabric layer, the user is allocated virtualized hardware. Thus, each user may be given the responsibility of satisfying their own software dependencies, supplied in their own OS submissions.

- Virtualization may enable the utilization of public computing resources, such as university computer labs or an organization's workstations. While one part of a workstation serves the original purpose of providing a tool for students' or employees' work, another part may serve as a computational resource for a grid, for example during the night when they usually are not used, or otherwise during low utilization.

- Encapsulation allows the monitoring and provisioning of hardware resources. This further allows the account keeping of VOs' resource usage, and resources can be brokered between VOs.

- Upgrades to OSs and software can be done on virtualized hardware without bringing down the computer. In a transitional phase, both old and upgraded OSs may run simultaneously on the same computer, allowing upgrades without downtime.

The potential drawbacks of virtualization are also worth mentioning. Multiple processes running simultaneously on the same CPU lead to the cache being overwritten subsequently by the processes. This is often referred to as *thrashing* of the cache and leads to poor utilization of the cache and a significant slowdown. Naturally, processes running simultaneously in different OSs on the same CPU will lead to the same problem. Thus, running two OSs simultaneously on a single CPU is not considered beneficial in HPC when running computations, in terms of resource utilization.

# Chapter 2

# Background

An OS is a complex piece of software. It manages the computer hardware and provides a foundation on which user application software can run. All the hardware devices of a computer, such as harddrives, network interface cards, keyboards and monitors are managed by the OS. Also, the OS abstracts an interface to memory management, processes, timers and file systems in order to make programming of user application software easier. Without an OS, a computer is essentially useless.

Xen is in many ways similar to an OS. It provides a foundation on which OSs can run, and, similarly to an OS, it has to manage the computer directly. Programming Xen therefore requires knowledge about the computer architecture it is programmed for. Xen is programmed for the  $x86^{1}$  architecture. Knowing the x86 architecture is therefore necessary in order to understand the design of many parts of Xen software, which are specifically programmed for the x86 architecture. The x86 architecture is presented in Section 2.2.

Knowing the  $IA-64^2$  architecture is of course necessary when programming system software for it. Therefore, in order to understand how the IA-64 architecture is different from the x86 architecture and how system programming is affected by these differences, an introduction to the IA-64 architecture is given in Section 2.3. The two architectures do, however, have many similarities, which are basic in many commodity computer architectures. Therefore, some essential concepts of commodity computer architecture are presented in Section 2.1.

Xen is originally designed with the x86 architecture as the target environment. The x86 architecture was, however, probably never intended to support virtualization. This makes efficient virtualization of the architecture difficult to achieve, which is part of the reason why this has not been achieved with a near-to-native level of efficiency until recently. Guest OSs that run in the Xen system are modified to achieve high efficiency. Still, they let user applications run unmodified. Thus, many aspects of the original OS need to remain intact in order to still support their interfaces to the user applications. Xen must

<sup>&</sup>lt;sup>1</sup> The term x86 usually refers to Intel, AMD or other chip manufacturers' PC architectures that are backwards compatible with the 80386 architecture, except for the ones that use 64-bit extensions, namely AMD's Opteron and Intel's EMT64 technologies. The term *IA-32* is also often used.

$<sup>^2\,</sup>$  The term IA-64 refers to Intel's Itanium processor series, also referred to as Itanium Processor Family (IPF).

therefore facilitate for many aspects of a traditional OS such as memory management, device drivers and I/O. How Xen provides an efficient platform for virtualization is discussed in Section 2.6.

Xen heavily leverages code from Linux both in the virtualizing software and in guest Linux kernels. Understanding Linux helps to understand some general OS concepts and how Xen virtulizes hardware. Also, this helps to understand how guest OS are modified to run on Xen. A description of some important aspects of the Linux OS kernel is given in Section 2.4.

Some important principles in virtualization govern the development of Xen and are important guidelines that are necessary to follow when implementing on complementary architectures. Also, looking at other VMM technologies may help the understanding of Xen. Some important principles of virtual machines are discussed in Section 2.5, along with some state of the art examples of virtualization technologies.

## 2.1 Commodity Computer Architecture

The von Neumann model is by far the most prevalent paradigm for modern computer architectures. It specifies a processing unit and a storage unit, which cooperate to run a program. Indeed, the most common computer architecture on desktop computers in use today—the PC, or in more technical terms, x86, architecture (see Section 2.2)—is an architecture which stems from the von Neumann model.

X86 processors are usually relatively cheap and common and are therefore often called *commodity hardware*. Commodity computers such as the PC are popular in offices and private homes and are in these contexts used for diverse applications, such as word processing, games and multimedia. The rich requirements of these applications have evolved commodity desktop computers into powerful all-round computers, capable enough to be used in mainframe computers, both in application servers and scientific computations. Commodity hardware can be attractive in many HPC applications as well as desktop applications, but mainly because of its low total cost of ownership compared to specialized computer hardware. Integrated circuit technology evolves to allow transistors to be ever smaller, and new applications for commodity processors are realized. Recently, commodity computer architectures such as the x86, have been used also in embedded devices, showing how diverse applications evolve as integrated circuit logic becomes cheaper, less power consuming and smaller.

For some critical applications, however, commodity hardware might not suffice, or other computer architectures may give significant performance benefits compared to what x86 computers have to offer. While simply relying on the predictions of Gordon E. Moore [Moo65], that time can let computers catch up with the performance demands, for a long time often has been a practical solution, alternative architectures may provide benefits beyond what next generation x86 processors give. Intel aims, with the IA-64 architecture (see Section 2.3), to provide a set of architectural improvements in a new computer architecture more or less independent from the x86 architecture.

One thing that separates commodity computers from many other computers is the need for a diverse set of ways to interface with the human user, in order to satisfy the user's diverse set of requirements. This has played an important role in the development of processor architectures. Many features exist to satisfy users' interaction with the system, to support a diverse set of applications and to increase performance of the system without asking too much of the system programmer. Some of these features are described in the following sections. *Interrupts* are the processor's method of communicating the event of a user interaction with the system to the processor, which is further discussed in Section 2.1.1. *Privilege separation* allows the system to be protected from programming mistakes, as discussed in Section 2.1.2. Being von Neumann architectures, commodity architectures also employ schemes for managing storage, which is discussed in Section 2.1.3.

#### 2.1.1 Interrupts

In order for a computer to be useful it needs to be able to handle input from users and react to it. For instance, when a user types a character key on the keyboard, she expects the computer to react to it by for instance showing the typed character on the computer display. Similarly, the OS needs to be notified when a DMA (Direct Memory Access) transfer has completed or a packet arrives on the network, in order to react to it. When the processor receives the electrical signal that indicates the press of a certain key or the completion of a DMA transfer, it then interrupts the current running process and executes an *interrupt* procedure.

Interrupts are either *maskable* or *nonmaskable*, that is, either they can be disabled or they can not. Critical events, such as hardware failures, often give rise to nonmaskable interrupts. The procedure which a particular interrupt is to execute is called an Interrupt Service Routine (ISR). When an interrupt occurs, a special table is referenced, indexed by the types of interrupts, and the ISR corresponding to the interrupt is executed or called.

All devices that deliver interrupts are connected to an *interrupt controller* by an *Interrupt ReQuest (IRQ)* line. Whenever a device needs to interrupt the processor it raises an IRQ signal, telling the interrupt controller that it is ready to perform some operation. In basic terms, an x86 interrupt controller further

- stores a vector corresponding to the received signal into its I/O port,

- issues an interrupt to the CPU by raising a signal on the INTR pin,

- waits until the CPU acknowledges the interrupt and then clears the INTR pin.

The number of IRQ lines is limited, thus some devices share IRQ lines. IRQ sharing is achieved by having one ISR per device that uses a particular IRQ. Since the ISR does not know initially which device issued the interrupt, each ISR related to the particular IRQ is executed; however, each ISR first checks if it was its particular device that generated the interrupt. Another way devices share IRQs is by multiplexing them in time.

The processor does not only interrupt itself on external impulse. It may also issue interrupts when an instruction is erroneous or otherwise problematic, for instance on divide-by-zero errors or page faults. These internally generated interrupts are usually called *exceptions* rather than interrupts.

#### 2.1.2 Privilege Separation

In a multi-user time-sharing OS there is a need to protect the underlying execution environment from malicious or erroneous use. For instance, normal users should not be allowed to alter the execution of kernel or other users' processes. Also, faulty user programs should not be able to break the execution of the kernel by, for instance, altering memory reserved for kernel processes. Thus there is a need for protecting the memory reserved for the kernel through a privilege separation mechanism. Similarly, certain instructions should only be allowed to be executed and, certain registers should only be allowed to be accessed by the kernel.

Commodity workstation and mainframe computer processors maintain privilege separation through protection of memory segments or pages (see Section 2.1.3). The protection information for a segment or page is stored as metainformation which is compared to the running process' privilege level. Also, certain registers and instructions, which, for instance, control the processor's operation or interaction with other hardware, are protected.

The currently running process' privilege level, usually referred to as the *Cur*rent Privilege Level (CPL), is kept in a register, which also allows the processor to check if the process is allowed to execute certain instructions or access certain registers. If a process with insufficient CPL tries to access protected registers or execute protected instructions, a *Privilege Operation fault* is raised by the CPU, which may be handled as any other exception and recovered or ignored.

#### 2.1.3 Memory Management

Memory is usually addressed differently from a processor and from a user program's point of view. Managing memory directly by its physical addresses makes programming complex; intstead, the OS may allow memory to be accessed through *virtual* addresses. In a virtual addressing scheme, when an application addresses a particular memory location, it provides a virtual address, which then is translated into the corresponding physical address of the memory location.

There are different ways to virtualize memory access. The two most prevalent in commodity computer architecture are *segmentation* and *paging*. Segmentation is a technique for logically arranging memory such that different processes accessing memory do not interfere with each other, thus making programming easier and more secure. Having privilege separation on a segment lets certain processes have access to segments that other do not.

Through paging, memory is arranged into pages, which are disjunct memory ranges that are contiguous in physical memory and in the way they are presented as virtual memory. Similar to a segment, a page may demand that accesses to it are privileged. The difference, however, between segmentation and paging, is that when using segmentation, the program explicitly addresses and manipulates the segments, while using paging, the program uses a virtually linear address space which may be non-contiguous in reality. Segmentation and paging in the x86 architecture is described in Section 2.2.1.

In order to translate a virtual address into a physical address the OS looks up the address in a *page table*. The page table is a data structure stored in main memory, which stores the addresses of the individual pages. The procedure of

Figure 2.1: Virtual address to physical address translation.

translating a virtual address into a physical address is illustrated in Figure 2.1. As the number of pages is potentially very large, the data structure is expanded into a hierarchy. The top data structure is a *page directory*, which further holds several page tables. When a virtual address is translated through the page table, the *directory* part of the address points to a page table entry in the page directory. Further, the *table* part of the address points to a *Page Table Entry* (*PTE*) in the page table. Finally, the last part of the address is used as an offset within the page, which is the physical address translation of the original virtual address. This hierarchical scheme allows for not allocating memory for page tables until they are actually used, reducing the page table memory profile proportional to the number of pages used, rather than the number of pages in the whole virtual address space.

Having to look up addresses through main memory, however, is a costly affair. Given that a virtual to physical address translation may take two or more memory lookups in addition to the intended physical one, looking up the page directory, page table and possibly higher level data structures, the overhead of a pure main-memory approach is significant. Most processors therefore employ a *Translation Lookaside Buffer (TLB)* in order to speed up virtual address translation. The TLB acts as a cache, storing a subset of the possible translations, after a possibly speculative scheme with regards to which translation is most likely to occur next. As the TLB is implemented physically close to the core of the CPU, with high-speed logic, translations are performed with a significant speedup compared to translations through main memory. TLBs are, however, limited in the number of translations they can keep. The first time a translation is used, it must be found in the page table, with the same memory access overhead. Also, as new translations are used, they will replace older ones, which again may need to be translated through memory in the future.

### 2.2 The x86 Architecture

The x86 architecture fits quite nicely under the CISC (Complex Instruction Set Computer) paradigm. Traditionally, computers that fall under this paradigm, in contrast to RISC (Reduced Instruction Set Computer) computers, afford a less rich register set due to a higher richness in ISA (Instruction Set Architecture) complexity. Even though modern x86 CPUs may afford a richer register set, backwards compatibility often dictates that new registers are redundant.

Segmentation was the first memory management paradigm in the x86 processor. It remains a legacy from the processors that were developed before the 80386 processor. The 80386 processor introduced paging, which allowed the use of virtual memory. The x86 processors of today therefore support both segmentation and paging for managing main memory. How segmentation and paging of memory is managed in the x86 CPU is discussed in Section 2.2.1.

In Linux, control of the CPU is handed between programs through a mechanism called *process switching* (see Section 2.4). When control is handed from process p to process q, the x86 CPU can automatically store some of the registers that are used by p, or p's *hardware context*, to memory. After q is finished, and p is given control of the CPU again, the CPU automatically loads p's hardware context from memory into the registers. In the case of segment registers and general purpose registers, this is further discussed in Section 2.2.2. Hardware management of FPU (Floating Point Unit) registers is discussed in Section 2.2.3.

The x86 processor as used in PC's has to interface with many different types of hardware. Hardware which is external to the CPU, can be communicated with through a set of different interfaces. I/O ports are the addresses which some devices are connected through. The I/O ports can be accessed either through special instructions, or they can be mapped in the physical address space. Also, as discussed in Section 2.1.1, devices deliver interrupts to the CPU to notify of certain events. The CPU also notifies itself about certain events, such as divide-by-zero errors and timer events. Interrupts are further discussed in Section 2.2.4.

#### 2.2.1 Memory Management

Backwards compatibility has always been preserved in the x86 series architectures. Though segmentation strictly is not necessary for most modern applications, as it is made redundant by paging, the x86 maintains segmentation in order to allow support for existing software that uses segmentation. Segmentation was introduced to make memory management safer and more scalable, by encouraging or making it easier to manage separation of memory spaces between user space and kernel space and between code and data. This was achieved by having different, although possibly overlapping, memory segments for data and code and assigning them different privilege levels, giving heritage to *rings*, as illustrated in Figure 2.2. In Linux, only privilege levels zero and three are used, in which Kernel Mode and User Mode processes run, respectively. These privilege levels are commonly referred to as "rings".

Attributes of a segment, such as its size, its physical starting address and the privilege level required to access it, are stored in its segment descriptor. Segment descriptors are stored either in the Global Descriptor Table (GDT) or the Local Descriptor Table (LDT), which are data structures in memory.

Figure 2.2: Privilege separation in Linux on the x86 architecture.

Segment selectors are used to reference the segment descriptors in the descriptor tables. A segment selector points to a specific segment descriptor in the GDT or LDT through an index and a flag that specifies whether the segment descriptor is in the GDT or in the LDT. The segment descriptor defines the level of privilege needed to read or write to its corresponding segment in the Descriptor Privilege Level (DPL) field.

To make segment addressing faster, the segment descriptor of the currently used segments are stored in segmentation registers. A particular segmentation register, which holds the segment identifier of the currently used code segment, namely the **cs** register, is significant because it also includes a 2-bit field called the Current Privilege Level (CPL). This field keeps the privilege level of the current executing process, one in the range zero through three. Level zero is the most privileged and allows access to all processor registers and to hardware device interfaces. Also interrupt handling instructions are instructions of privilege level zero . Intel's intention of rings one and two is for having the OS run device handling routines in these levels; however, they are rarely used. Ring three gives access only to a limited set of registers and instructions, excluding interrupt handling instructions and hardware device interfaces.

As segments have differentially privileged access, so do pages, though only two different levels, "User" and "Supervisor". Pages that are flagged "User" may be accessed by any process, while pages that are flagged "Supervisor" may only be accessed by a process when the CPL is less than three.

The pointer to the top level page directory of the current process is kept in the cr3 control register. Whenever the address space needs to be changed, such as, for instance, after a process switch, the address of the next process' page directory is written to the cr3 register. This, at the same time, triggers a flush of the TLB, invalidating all the TLB's translation entries.

#### 2.2.2 Process Switching

The x86 CPU can automatically manage the contexts of different processes. It offers a mechanism for storing a complete CPU state except for FPU and *Streaming SIMD Extensions (SSE)* (see Section 2.2.3) states. The most essential registers that comprise this state are (see Appendix A.1):

- The segment registers—CS, DS and others.

- The general purpose registers—EAX, EBX, ECX and similar.

- The pointer to the last executed instruction—EIP.

- The pointer to the page directory—CR3.

- The pointer to the Kernel Memory Stack (see Section 2.4.4)—ESP.

In order to manage this state, the CPU uses a special segment called the *Task State Segment (TSS)*. This is the segment in which the context of a process is stored upon an automatic process switch. The TSS's segment descriptor is called the *Task Gate Descriptor*, which can be stored in a GDT, an LDT or an *Interrupt Descriptor Table (IDT)* (see Section 2.2.4). By performing a far JMP or CALL instruction, a task may target any segment visible to it through a GDT, LDT or IDT. As a task enters a segment its CPL is compared to the segment's DPL. If the CPL is more or equally privileged than the DPL the task is allowed to continue, and the CPL assumes the DPL. If the targeted segment is the TSS, the CPU automatically performs a hardware context switch.

#### 2.2.3 The Floating Point Unit

The floating point capabilities of the x86 architecture has evolved with the demands for more faster and more efficient floating point calculations in 3D games, multimedia and HPC. The architectures that x86 is based on, started out without floating point capabilities, and the x87 floating point co-processor was later added to extend the processors, with floating point arithmetic capabilities. The external x87 co-processor was accessed as other external devices and results were returned with external interrupts. The FPUs of modern x86 processors are still logically x87 co-processors, although they are now integrated into the circuits of the CPU and thus much faster. Also, later, with the Pentium processor, the MMX extension allowed the FPU to be utilized more efficiently, directly through MMX registers. In addition, the Pentium III processor introduced the SSE extensions, which perform floating point arithmetic in the XMM registers, which are separate from the FPU registers. SSE allows one operation to be executed on multiple vectors in parallel in a single instruction unit. The SSE extensions have also evolved, and recently SSE2 and SSE3 extensions are included in Intel's x86 processors.

The x86 processor still generally performs floating point arithmetic in the FPU. The registers of the FPU are utilized either through esc instructions or, as of the Pentium processor, alternatively through MMX instructions. On a hardware context switch, the processor does not automatically save the FPU or XMM registers in the TSS as with general registers, so the OS needs to store and restore these registers manually. The processor does, however, help the OS

to save these registers only when needed, that is, only when a process really uses the FPU or XMM registers. That is, the FPU and XMM state is *lazily* managed.

In the CRO register (see Appendix A.1), the TS flag indicates whether a context switch is performed, and on every hardware task switch the TS flag is automatically set. The TS flag may also be changed manually, although this requires a CPL of 0. When a new task executes it may or may not use the FPU or XMM registers. If it uses the FPU, the processor will issue an exception, telling the OS that the FPU context has not yet been loaded. The OS may then proceed to manually load the FPU context from the TSS and clear the TS flag. Further attempts to use the FPU or XMM registers will not raise exceptions as long as the TS flag remains cleared. If the process does not use the FPU, however, a FPU context switch is not necessary.

#### 2.2.4 Interrupts

A wide range of external devices are connected through a *Programmable Inter*rupt Controller (PIC). The traditional PIC hardware has a few limitations, such as lack of support for SMP. It has later been replaced with the Advanced Programmable Interrupt Controller (APIC), which is bacwards compatible with the traditional PICs but has support for SMP. All interrupts—including exceptions—in the x86 processor are handled through the Interrupt Descriptor Table (IDT). Interrupts of external devices are handled by the ISRs as IRQs. Pointers to the ISRs of the interrupts and exceptions are stored in the IDT.

Examples of exceptions are *General Protection Fault* and *Page Fault*. The General Protection Fault is raised whenever the protection mechanisms of the processor are violated, for example, if a user process crosses into ring zero. The process should then be notified and possibly terminated. Page Faults are raised whenever a page that is referenced, is not present in the page table. The OS should then take the necessary actions to correct the page table and resume the execution of the faulting process.

One of the most important external interrupts is perhaps the timer interrupt. It is assigned the IRQ number zero on all x86 processors and is necessary, for instance, to share the time of the processor between processes, by interrupting a process when it has used a share of its time. The x86 processor offers a set of hardware mechanisms for letting software know the time:

- The *Real Time Clock (RTC)* is a clock that keeps wall clock time and runs even when the computer is powered off.

- The *Time Stamp Counter (TSC)* counts the number of CPU clock cycles since the computer was turned on, i.e. it runs with the same frequency as the CPU and accumulates from zero.

- The *Programmable Interval Timer (PIT)* can be programmed to deliver interrupts at a given time frequency.

- The *CPU Local Timer* is similar to the PIT, however it only delivers per CPU interrupts and is only present in recent x86 processors.

### 2.3 The IA-64 Architecture

The Intel Itanium architecture is one of the participants in the great 32-bit to 64-bit leap, which has had a significant impact on the processor industry the last couple of years. While AMD have chosen a 64 bit extension of the x86 architecture, Intel early decided to break with the old<sup>3</sup> x86 architecture and release the new 64-bit IA-64 architecture through the Itanium processor series.

The Itanium's shift from the x86 architecture introduces a new paradigm for programming, which Intel calls *Explicitly Parallel Instruction-set Computing (EPIC)*. A good introduction to the EPIC paradigm is given by Mark Smotherman [Smo02]. This new architectural paradigm shifts the responsibility of optimizing the execution of programs from the CPU over to the compiler or assembly programmer. The compiler or assembly programmer has the responsibility of programming explicitly parallel programs, specifying which instructions may execute in parallel, as opposed to Pentium architectures, where the CPU decides the issuing of instructions. At the same time, the IA-64 architecture has similarities to certain RISC architectures. Among other things, the IA-64 CPU has a large number of registers. Further features of the IA-64 architecture are summarized in Section 2.3.1. The IA-64 register set is discussed in Section 2.3.2.

The IA-64 processor's interface to hardware has had the opportunity to be designed from scratch, independently from legacy x86 interfaces, such as the BIOS (Basic Input Output System) and the PIC. This makes the new IA-64 hardware interfaces easier to program. The IA-64's equivalent to the BIOS, the *Extensible Firmware Interface (EFI)*, is described in Section 2.3.3. This is followed by a description of the IA-64 architecture's interface to interrupts, in Section 2.3.4.

Like the x86 architecture, the IA-64 architecture employs paging of memory. In order to make virtual address translation more efficient, it also employs a TLB. The IA-64 TLB is, however, more sophisticated and allows flexible management of address spaces. Also, maintaining compatibility towards x86 software, it has support for segmentation, in IA-32 compatibility mode. Memory management in the IA-64 architecture is further discussed in Section 2.3.5.

Some computer architectures provide dedicated facilities for monitoring system performance, such as the UltraSPARC series' Performance Control Register and Performance Instrumentation Counter  $[E^+98]$ . The original 80386 specification did not include support for CPU performance monitoring. Support for this has been added later, and some of the x86 series' models, particularly newer models, do have performance monitoring facilities. These are, however, often obscured, sometimes intentionally, being unstandardized and undocumented. The IA-64 architecture makes performance monitoring easier, with its *Performance Monitoring Unit (PMU)*, which is discussed in Section 2.3.6.

#### 2.3.1 Key Features

The Itanium incorporates a set of features that separate it from traditional architectures. These features play a part in defining the IA-64's ISA. One of the most distinctive features is the concept of *predication*. This is one of the features

<sup>&</sup>lt;sup>3</sup>While some argue that the x86 architecture is too old and complicated after many patches and extensions, others argue "Don't fix it if it's not broken".

| 41 bits            | 41 bits            | 41 bits            | 5 bits   |

|--------------------|--------------------|--------------------|----------|

| Instruction slot 2 | Instruction slot 1 | Instruction slot 0 | Template |

Figure 2.3: The format of a bundle.

which exposes the programmer with the explicitness of the EPIC paradigm. Predication avoids costly branch prediction misses by executing the resulting instructions of either condition—true or false—of a conditional branch while committing only the result of the condition which was eventually met.

Two other important concepts of the IA-64 ISA also expose the explicitness of the EPIC paradigm, namely groups and bundles. The software programmer is given the responsibility of exploiting the instruction level parallelism of the architecture. Instructions are issued one bundle at a time, and the instructions in a bundle may be executed in parallel, with a few exceptions. One bundle consists of up to three instructions, but rules define which instructions may be bundled together.

The structure of a bundle is illustrated in Figure 2.3. Three instruction *slots*, each 41 bits wide, can each hold an instruction. Several different types of instructions are defined [Intb]:

- Memory (M)—memory instructions.

- Integer (I)—integer instructions not using the ALU.

- Integer (A)—integer instructions using the ALU.

- Branch (B)—branch instructions.

- Floating point (**F**)—floating point instructions.

- Extended (L+X)—allows 64-bit immediate values to be used, as it spans two slots.

A *template*, residing in the least significant five bits of the bundle, defines what type of instruction is inserted into each slot. For instance, the template 0x10 defines that slot 0 is an **M** instruction, slot 1 is an **I** instruction and slot 2 is a **B** instruction.

The structures defined by these templates are governed by the availability of execution units in the processor. If a set of instructions require the use of a particular type of execution unit, and there are n units of this type available, then n instructions from this set may execute in parallel. In this case, a template will define that a bundle may consist of up to n of these instructions.

Grouping of bundles further allows instructions to execute in parallel. When a set of bundles are grouped together, the processor assumes that the instructions in these bundles have no dependencies and may be executed in any sequence, be it sequential or parallel. The IA-64 architecture specifies a large number of registers. The general integer and floating point register files both have 128 registers. A potential problem of having a large number of registers is that a large state may need to be stored in memory on each context switch, which is a slow process relative to CPU speed. How the large set of registers is managed in the IA-64 processor is discussed in Section 2.3.2.

Programming for the IA-64 architecture differs significantly from x86 programming. Still, the IA-64 architecture allows x86 programs to run in an *IA-32 compatibility mode*. This mode, however, does not take advantage of some of the IA-64's performance critical features. For example, explicitly parallel programming for the IA-64 architecture is not possible given the x86 ISA. Thus, the IA-32 compatibility mode is provided mostly for backwards compatibility towards legacy programs.

#### 2.3.2 Registers

In RISC processors, *register conventions* are needed to dictate how OSs are to use and manage the registers. This is also adopted by the IA-64 architecture. The set of registers in an IA-64 CPU is divided into several *register files*. The *General Register File* consists of 128 64-bit registers, R0 through R127. These are general purpose integer registers. They may be used freely, only constrained by conventions, except for R0, which is always zero. Convention states that they are divided into two classes, *preserved* and *scratch*. Preserved registers must be explicitly managed by any process that uses them, that is, on any function call, the process must itself store the necessary registers in memory. Scratch registers, however, are at a process' disposition to use at convenience.

The IA-64 architecture provides the programmer with the illusion of an unlimited register stack through a mechanism called the *Register Stack Engine* (*RSE*). It makes utilization of the general register file easier for programmers. It presents the programmer with a logical *register stack frame*, which consists of a range of allocated registers. Whenever a branch is executed, the allocated register stack frame is stored on the stack, and upon return from the branch the state of the allocated registers is restored from the stack. Registers R32 through R127 are used by the RSE on Itanium, and any number of registers within this range may be allocated to a register stack frame.

The register stack stores and retrieves register frames in main memory in a LIFO (Last In, First Out) manner. Register stack frames stored in memory can also be accessed directly in memory. The BSP application register points to where the beginning of the current register stack frame would be in memory if it were to be put on the stack.

As in the x86 architecture, floating point registers may be managed lazily in the IA-64 architecture. This may be achieved by disabling access to these registers, which will cause an exception when a task tries to access them.

#### 2.3.3 Hardware Abstraction

The IA-64 architecture abstracts away small differences in different hardware implementations through three interfaces called *Extensible Firmware Interface* (*EFI*), *Processor Abstraction Layer* (*PAL*) and *System Abstraction Layer* (*SAL*).

The EFI maintains an interface for booting an OS kernel called *EFI boot* services. This includes services for allocating and freeing memory. These services are accessed in physical addressing mode only. This is used by OSs for booting.

The routines for the EFI, PAL and SAL interfaces are accessed through a table called the *EFI system table*, which points to the individual routines, in their respective memory spaces. An OS accesses these routines by looking up in the table and executing the routines directly. This table is defined by convention and must be followed by the OSs.

#### 2.3.4 Interrupts

Interrupts are similar in concept in the IA-64 architecture, to the x86 architecture. In the IA-64 architecture, the legacy of the PIC is no longer necessary to maintain. It is replaced with the *Streamlined Advanced Programmable Interrupt Controller (SAPIC)*, which allows faster delivery of interrupts and more CPUs in an SMP system. The IA-64 keeps interrupt handlers in a table called the *Interruption Vector Table (IVT)*. The starting address of this table is stored in the IVA register.

Similarly to the x86, the IA-64 architecture provides mechanisms for keeping time.

- The EFI provides an interface for reading wall clock time, similar to the x86's RTC, although abstracted.

- The Interval Time Counter (ITC) counts CPU cycles, similar to the x86's TSC.

- The *Periodic Timer Interrupt* allows the delivery of interrupts at a given frequency, similar to the x86's PIT.

#### 2.3.5 Memory Management

The IA-64 CPU uses a set of dedicated registers called *region registers* to make the TLB more efficient. They divide the address space into logically separate *regions*. Each entry in the TLB is tagged with a *region id*. On a TLB lookup, the entry of a region register is compared to the region id of the TLB entries. If the region id differs from the value in the region register, the TLB entry is invalid for this particular region. Thus, unlike in the x86 architecture, the TLB need not be flushed on address space changes, as invalid TLB entries are logically marked as invalid. The IA-64 TLB stores, in addition to address translations, protection information of the PTEs it stores. This information can be stored both as a part of the mapping entry in the TLB and in a separate *Protection Key Register* file. Protection information in the Protection Key Register file is accessed through the reference of a *protection key*. Every TLB entry has a protection key field.

The IA-64 architecture specifies two TLBs—one for data and one for instructions. These TLBs are both partitioned into a *cache* part and a *register* part. The cache TLB entries are hardware managed, while the register TLB entries are managed directly by the OS just like ordinary registers. Whenever a translation entry from virtual address to physical address does not exist in the TLB, the entry must be found in the page table. This can be a costly affair, as discussed in Section 2.1.3. The IA-64 architecture allows entries to be filled into the TLB more efficiently by using the *Virtual Hashed Page Table (VHPT)*. This feature is also referred to as the *hardware walker*.

For the hardware walker to function, it requires a logical second page table, formatted in a special way. There are two different supported page table formats, namely *short-format* and *long-format*. Using the long format, the OS uses a hash table as its page table, while using the short format, the OS must have a *virtually-mapped linear page table*. *Linear* means that the keys in the table are linear, so unlike page tables with several levels, which require one lookup per level, this table only requires one lookup. The table is mapped in virtual memory, residing in the virtual address space in each region in which it is enabled, thus it can also be mapped by the TLB.

When a virtual address, va, is to be translated to a physical address, pa, first the TLB is referenced. Given a miss in the TLB for va, in the traditional manner, a page fault would be raised, and the OS would walk the tables to find the PTE that translates va to pa—a costly operation. With the VHPT walker enabled, however, a miss in the TLB does not raise a page fault. Instead, the address of the PTE for va, va', is calculated by the walker. Since the VHPT resides in virtual address space, and given high spatial locality, the address of the PTE is with a high probability already in the TLB. Thus, only one extra memory lookup is needed. If the translation of va' does not exist in the TLB, a VHPT Translation Fault is raised, and the OS may continue to look up in the page table in the traditional manner.

An OS may also choose to skip the page table completely and avoid the protection mechanisms provided by paging and access memory directly, using physical addresses. The IA-64 CPU controls whether addresses are physical or virtual in the PSR register, using the DT flag (see Appendix A.2).

#### 2.3.6 The Performance Monitoring Unit

The IA-64 architecture offers, with the PMU, a standardized and documented facility for monitoring processor performance. The PMU is controlled by a set of registers that can be programmed to monitor certain performance aspects of the CPU. Two register files, consisting of the *Performance Monitor Data* (*PMD*) and *Performance Monitor Configuration* (*PMC*) registers, respectively, compose the PMU. The former register file captures performance data, such as number of processor cycles or instructions executed, while the latter controls what performance data the former captures.

The IA-64 architecture specifies eight PMC registers and four PMD registers and their semantics, though 248 PMC and 252 PMD logical registers are reserved for implementation at different IA-64 architectures' discretion. For example, the Itanium processor extends the PMU to include monitoring capabilities of TLB misses and branching characteristics, among others. The Itanium PMU allows a user to get the number of cycles or instructions used or the number of a particular instruction executed by a program, whether in user or kernel space or both; and to help finding hotspots, the location of where cache or TLB misses occured in code, can be captured.

### 2.4 Linux

Linux was initially intended by Linus Torvalds as a surrogate for the Unix OS on the x86 processor. However, its liberal licensing and the emergence of the Internet attracted many developers and allowed Linux to soon be ported to additional architectures such as MIPS, SPARC, Alpha, PA-RISC and, in 2000, IA-64. An important factor to the growth and popularity of Linux has been the availability of the free and open source GNU libraries and compiler. Comprehensive descriptions of the Linux kernels for the x86 and IA-64 architectures are given by the books "Understanding the Linux Kernel" by Daniel P. Bovet & Marco Cesati [BC02] and "IA-64 Linux Kernel - Design and Implementation" by David Mosberger & Stéphane Eranian [ME02], respectively.

Most modern OSs employ multitasking, that is, they allow multiple programs, or processes, to run simultaneously. For the OS to provide the illusion of running different processes simultaneously, it lets each process only to run for a very short period at a time, before switching to the next process. When switching to a new process, the kernel stores the register contents—the process' hardware context—in memory, then brings in another process by loading its hardware context from memory, and lets it run for a while, and so on. How the hardware context is managed when switching between tasks, is discussed in Section 2.4.3.

The timer is an important mechanism in an OS. It is, among others, used to interrupt a running process when it has used its time share, and pass control to the next process. The timing mechanisms in Linux are described in Section 2.4.2. The timer signals the kernel when it is time to switch processes through an interrupt. How the kernel handles interrupts such as these is described in Section 2.4.1.

Processes can have different privileges in terms of which memory segments or pages they are allowed to read or write and which instructions they are allowed to execute. The privilege levels are usually interpreted as protection rings, as shown in Figure 2.2, . Most OSs run in ring 0 while applications run in ring 3. In Unix terms these are called *kernel mode* and *user mode*, respectively.

As Unix, Linux has kernel and user processes. While kernel processes run exclusively in kernel mode, user processes run mostly in user mode but may also enter kernel mode through *system calls*. In order for user processes to do operations that require higher privileges, it has to enter the kernel through a system call. System calls are further discussed in Section 2.4.4.

Each process—that is, each address space—in Linux has its own page table, which is kept in physical memory. Linux keeps the page table tree in three levels, with a *Page Global Directory*, a *Page Middle Directory* and a *PTE Directory*. A page in Linux can be kept in main memory or moved to the swap space on a harddisk. The kernel tags a page which has been moved to the swap space as *not present*, as opposed to the case in which it resides in main memory, in which it is tagged *present*. Also, a page has information about read and write permission and the *dirty-bit* which signifies whether a page has been written to. These attributes are all kept in the page's PTE.

The traditional approach for finding performance hotspots in Linux is to instrument the code. Instrumenting, however, can have an influence on the execution of Linux and return results that are unrealistic, also certain low level functionality is difficult to monitor using software. The IA-64 port of Linux includes software for utilizing the PMU. This is further discussed in Section 2.4.5.

#### 2.4.1 Interrupts

The kernel manages many devices, such as harddrives, keyboards and network interface cards. Whenever such a device sends an interrupt to the processor, the kernel needs to readily respond. If any user space process is running, the kernel must suspend this process' operation and start executing the ISR corresponding to the interrupt. The operations of transferring control from a user process to the kernel and vice versa are called *kernel entry* and *kernel exit*, respectively. Kernel entry and exits are described in Section 2.4.4.

Some actions are time critical and have to be handled immediately, such as acknowledging an interrupt coming from the interrupt controller. To ensure that nothing interferes with the execution of a critical action, maskable interrupts are disabled during execution. Noncritical actions, such as reading keyboard input, however, are executed without disabling maskable interrupts. This allows more critical interrupts' ISRs to execute while less critical ISRs are interrupted and deferred until later. Some actions may even be deliberately deferred until later. On such interrupts, the action is only initiated in the ISR, and further execution continues outside the ISR at a later, possibly more appropriate, time. A high level description of how Linux handles interrupts is shown in Figure 2.4.

Actions that are deferred until later are based on a kernel mechanism called *softirqs*. These are used among others to deliver packets to and from network cards. Softirqs are executed dynamically by a kernel thread called *ksoftirqd*, which is short for *Kernel Softirq Daemon*. The Kernel Softirq Daemon runs in parallel with other kernel threads all the while during the kernel's lifetime.